请求页面 默认页 Article_Show.asp?ArticleID=32312 【内容】:

2021-08-09 11:11 作者:

写这篇文章时作者脑洞大开,提出了几个全新的概念,例如立方体集成电路Cubic IC,等时传输区域ITA,李特思空间LITS,有效功能体积EFV,阅读的时候,读者也需要打开脑洞,发挥想象力。因为是在公众号直接发表,没有经过同行评审和质疑,因此,就请广大读者作为这篇文章的评审者,对文章中的观点均可以质疑和提问,并通过留言和大家讨论。今天,这篇文章的内容或许有点超前!不过,要以发展的眼光看问题,十多年后,文章中有些看似异想天开般的描述在现实世界可能就会实现!摩尔定律刚提出的时候,我想摩尔本人也不相信在不到芝麻粒大小的一平方毫米,可以集成超过一亿只以上的晶体管~~

目 录

一. 以三维的视角设计集成电路

二. 对EDA工具的新要求

三. Cubic IC 设计方法学

四. 关于李特思空间 LITS 的描述

五. 关于有效功能体积 EFV 的描述

六. Cubic IC 和 3D Chiplet 的区别

七. 关于 Cubic IC 制造方法的预期

八. Cubic IC 带来的挑战

九. Cubic IC 能否延续摩尔定律

A BRAND NEW IDEA OF IC DESIGN

一 、以三维的视角设计集成电路

在传统大规模集成电路设计时,设计者把整个电子系统集成在一个芯片中,微处理器、模拟IP核、数字IP核,存储器或片外存储控制接口,都被集成在单一芯片上,形成一颗SoC上,并使用同一种工艺制造。

由于芯片上的集成是基于2D集成技术,即在晶圆平面上雕刻出纳米级的晶体管,随着系统复杂程度的提高,芯片的面积也会越来越大,这直接导致芯片良品率的下降。另外,随着工艺节点逼近物理极限,摩尔定律也日渐式微,人们亟需找到新的方法来延续技术的发展,SiP与先进封装技术、Chiplet与异构集成技术相继出现,成为延续摩尔定律的良方妙药。

今天,我们再进一步,提出一个新思路,即以三维的视角设计集成电路。

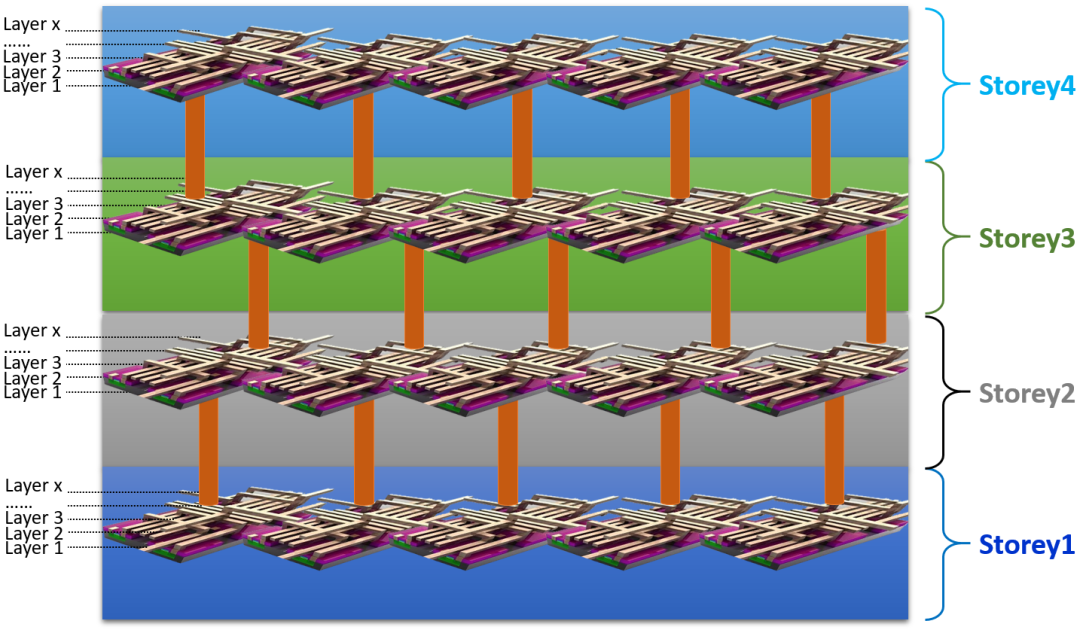

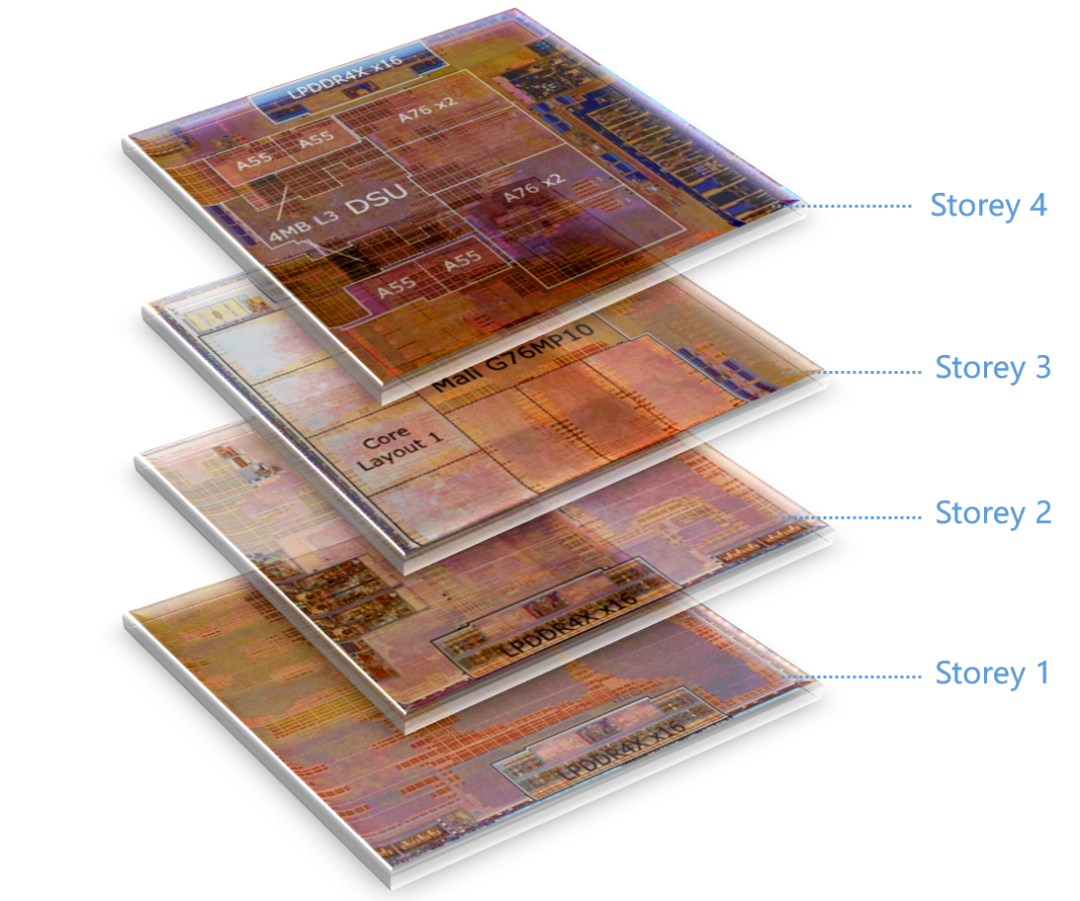

同样以设计一颗SoC为例,我们不再把微处理器、模拟IP核、数字IP核,存储器或片外存储控制接口设计在同一个晶圆平面,而是把他们分别设计在不同的楼层(Storey),然后再将这些楼层组合起来,形成一个完整的芯片,如下图所示。

从图中我们可以看出,每个Storey均有一层晶体管,并有多层布线将这些晶体管相互连接,不同的Storey之间采用TSV和RDL互连 (主要是TSV,RDL是在有些情况下,为了上下Storey金属互连对齐时用到) 。

对于不同的Storey (楼层) ,可以采用不同的工艺节点制造,同一个楼层上的晶体管,需要采用同样的工艺节点制造。

传统设计集成电路的人可能会想,Storey之间的互连是先进封装要干的事情。在本文中,情况发生了一些改变:从集成电路设计一开始,就要从三维的角度考虑进行设计了。

因为集成电路设计离不开EDA工具,因此,“新思路”的难点其实在EDA工具这一块,这也可以看成是集成电路设计和先进封装设计的融合,而融合的起点在于EDA设计工具的融合。

二、对EDA工具的新要求

传统的IC版图设计工具,先在硅基底上设计晶体管、电阻、电容等元器件,然后再通过多层布线将其连接,其网络互联和最终的布线都是在一个Storey上完成。

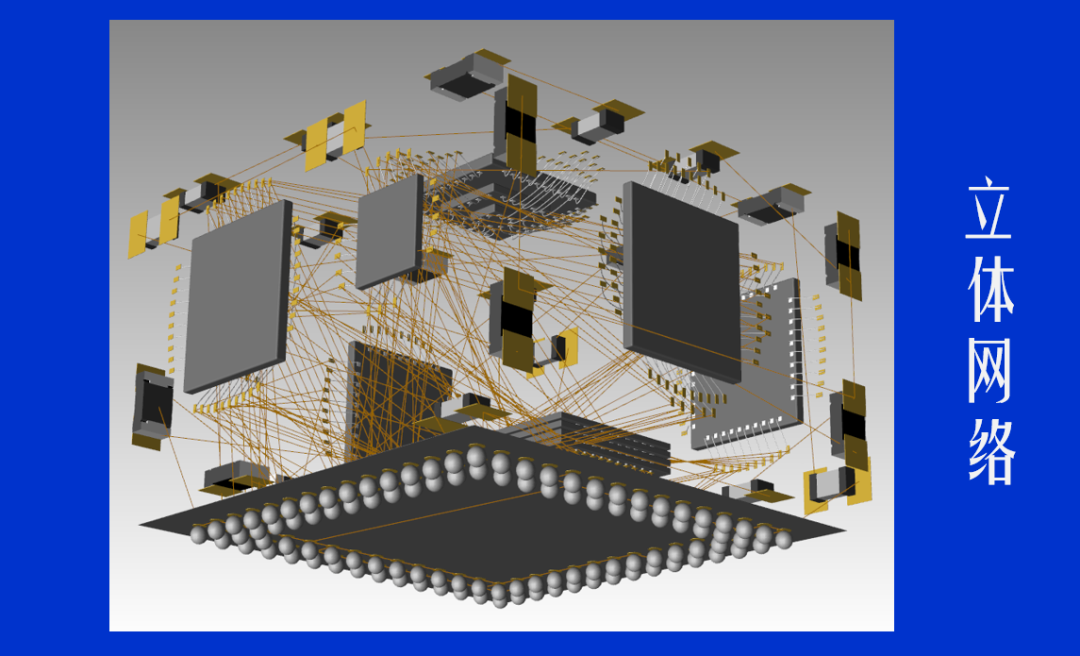

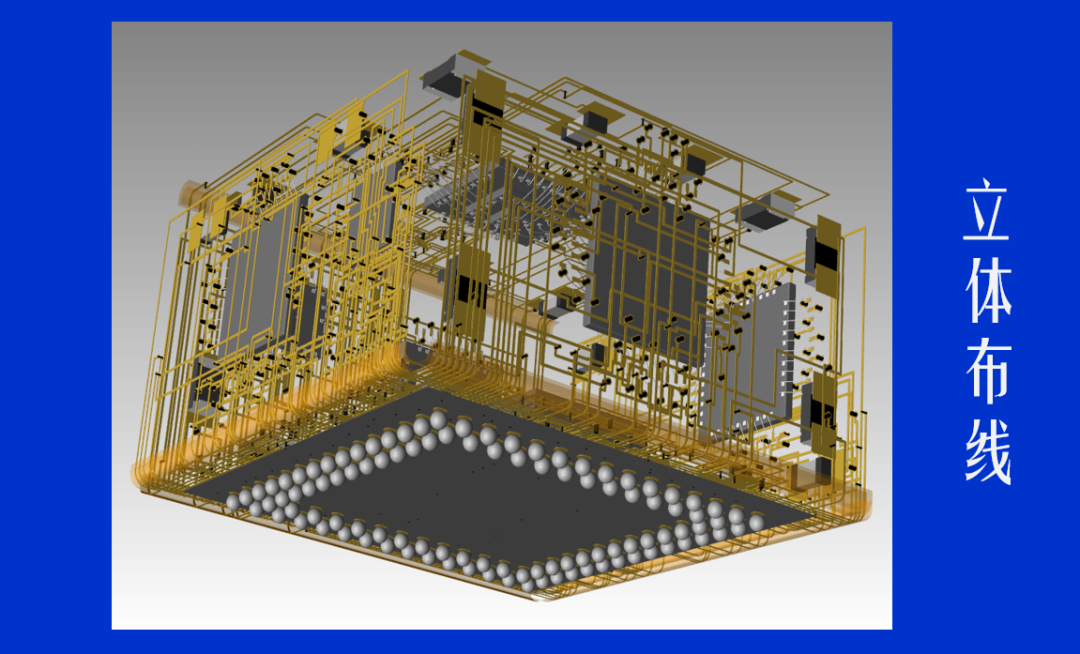

在新的设计思路下,由于存在多个Storey,因此,除了考虑Storey之内的网络互联和布线,还需要考虑Storey之间的网络互联和布线。因此其网络互联和布线均是立体的,我们可称之为立体网络和立体布线。

因为目前还没有EDA工具能够支持多个Storey这类的设计,因此无法找到确切的图形来描述。下面两张图可暂且作为一个近似的描述:元器件位于空间的不同位置,其网络的互联是立体的。

同样,当布线完成时,其布线也是立体的,除了Storey内部的元件需要布线连接,Storey之间也需要通过TSV和RDL连接。

从上面的描述我们可以看出,EDA工具需要具备多版图网络优化的能力,即能够在一个空间内,同时优化多个版图之间的网络连接,多个版图以虚拟堆叠的形式位于空间的不同Storey。同时,IC版图设计工具能同时处理多版图设计,多个版图可以位于同一个设计环境,也可以位于不同的设计环境,但多个版图之间的数据交互需要统一进行协调和管理。

目前,还没有这样的IC版图设计工具,但已经有类似的工具在先进封装设计中出现,具备近似的能力,例如Siemens EDA (Mentor)的高密度先进封装设计工具XSI和XPD之间的协同设计。

当然,除了设计工具,EDA仿真和验证工具也同样要跟上步伐。首先,对于设计工具构建的复杂数据模型,仿真和验证工具要能够正确解析。然后,仿真工具通过更强大的算法,进行仿真并得到正确的结果,验证工具则需要保证从设计到生产数据的正确性和精准性。

三、Cubic IC 设计方法学

上面描述的集成电路,有别与传统的基于晶圆平面的集成电路,我们给其起了一个新的名称:立方体集成电路 Cubic IC,可简称为CIC。

Cubic IC 由于其结构中包含了多个器件层,因此其设计方法和思路与传统IC是完全不同的。

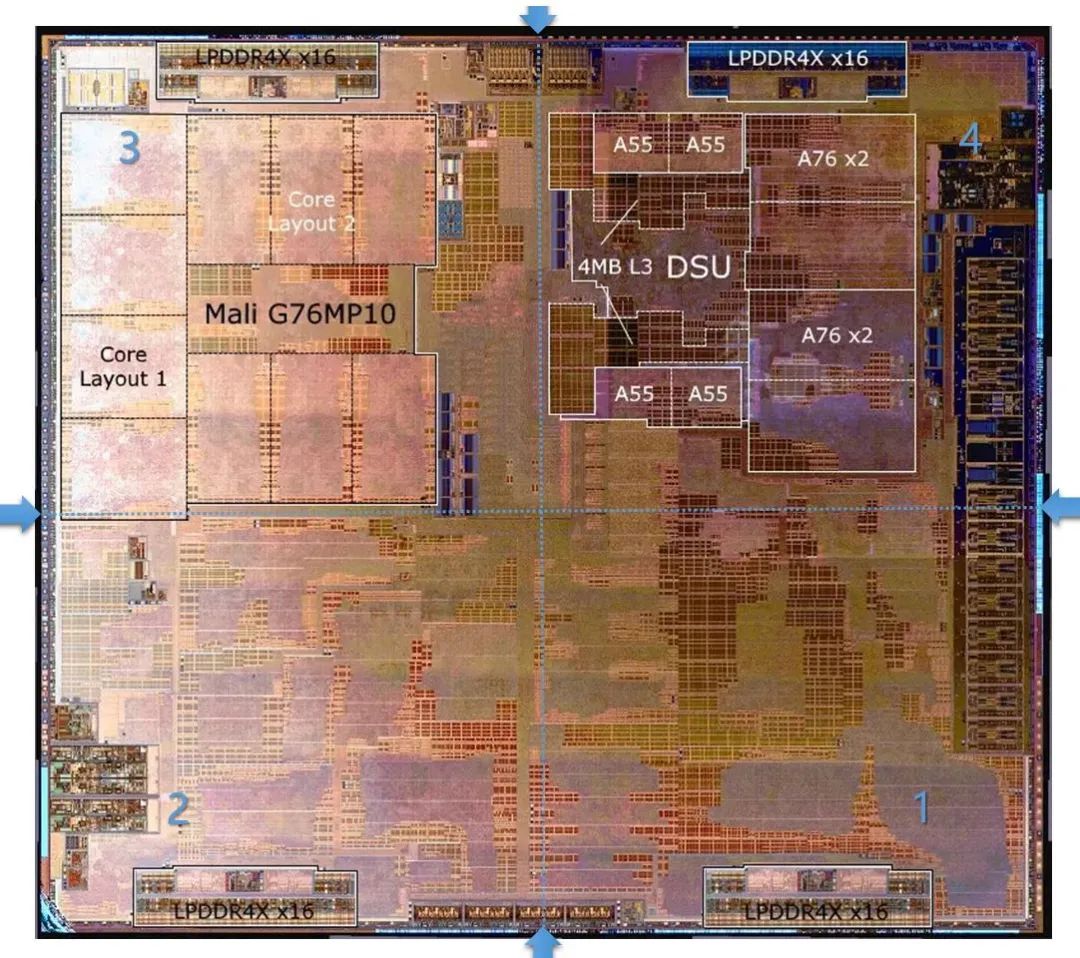

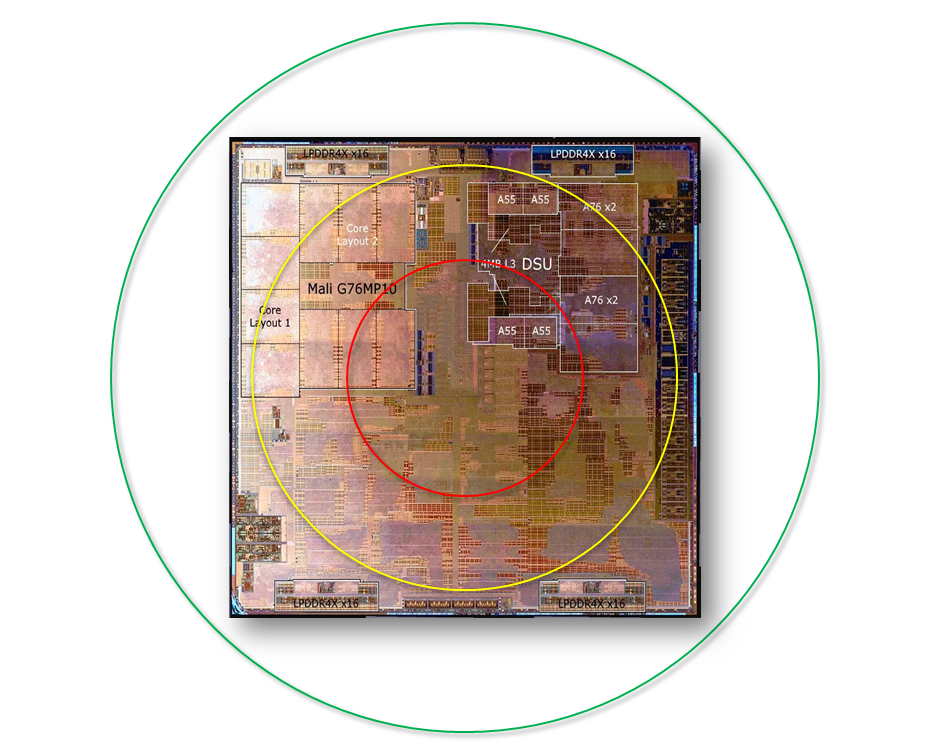

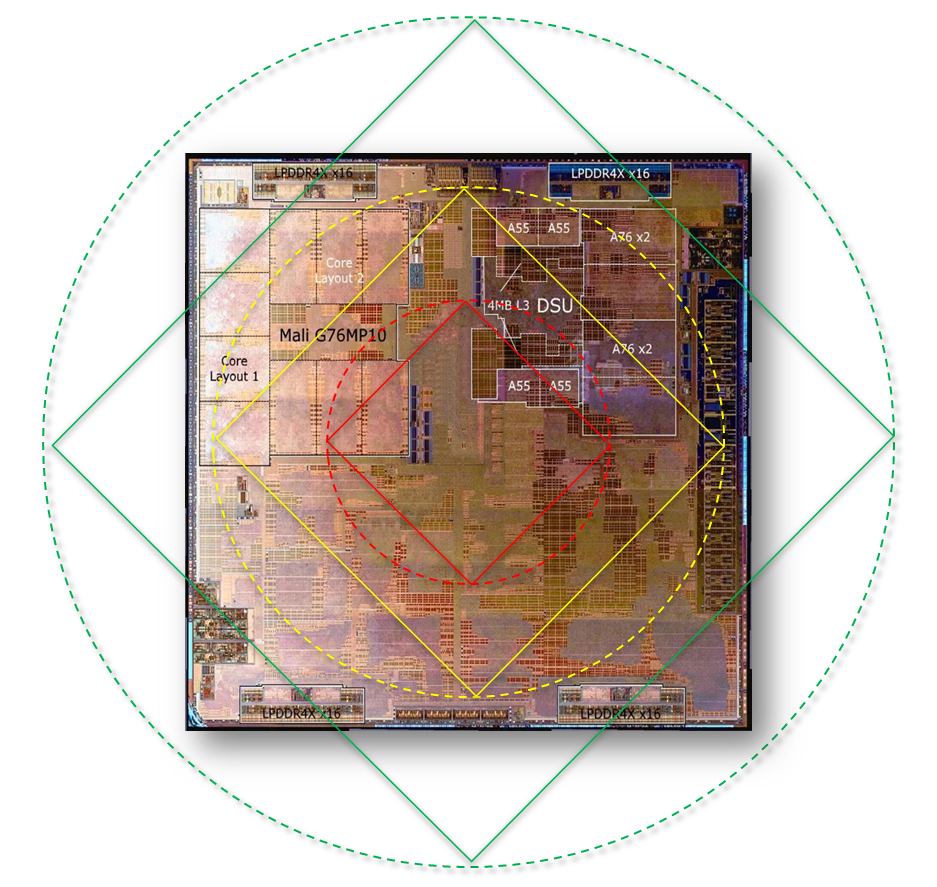

在传统IC的版图设计中,我们需要将不同的功能模块,按照2D的方式安排在版图的不同区域,如下图所示为海思麒麟980的版图设计。

按照 Cubic IC 的设计思路,我们可以将麒麟980的版图设计沿着浅蓝色的虚线分割成四部分,然后再将它们分别安排到不同的Storey,虚拟叠加起来,如下图所示。

每一个Storey内部的设计和传统的IC设计相同,各个楼层Storey之间,通过TSV和RDL相连接,在设计的过程中,需要进行整体规划和设计。

这样的话,芯片面积就减小为原有的1/4,并且由于采用了3D叠加方式,部分模块之间的互连距离更短,从而性能也会得到提升。

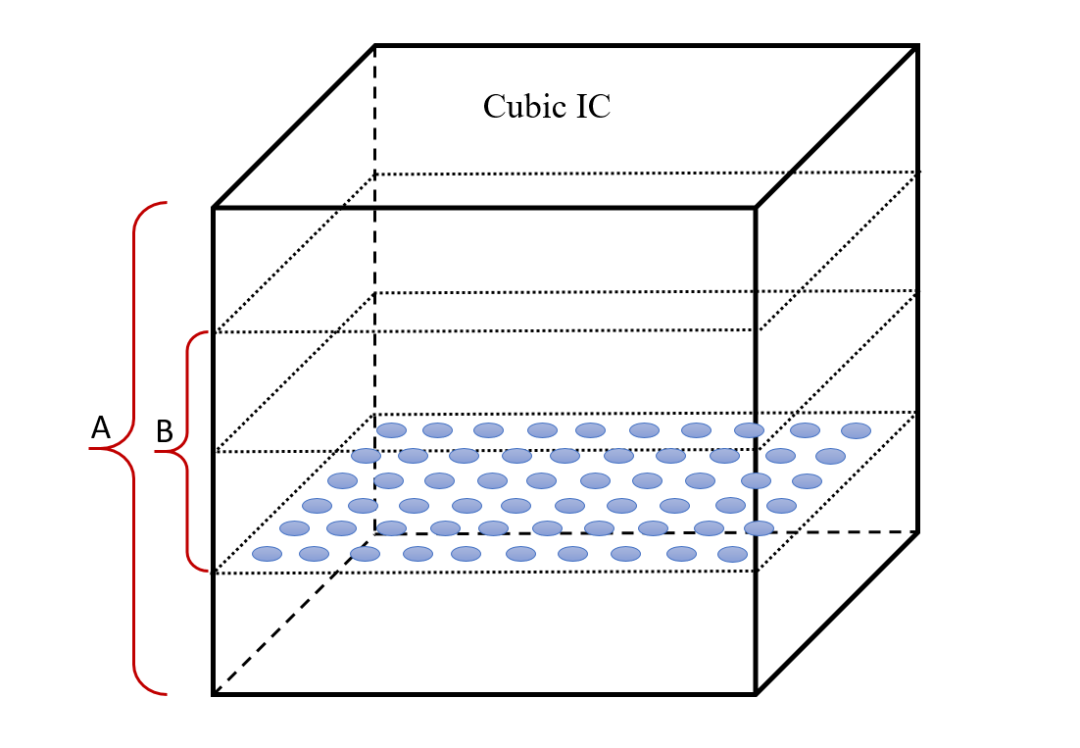

那么,最多可以叠加多少层呢?我们可以这么估算,Storey叠加的层数越多,芯片的面积就越小,一直到芯片堆叠的总厚度和芯片的长或宽的数值相当,即形成一个立方体,这也是立方体集成电路Cubic IC名称的由来。

我们以一个指尖大小的Cubic IC为例,假设其长和宽各为10mm,采用Cubic IC的设计思路,如果每个Storey减薄到50um,那么最多可以堆叠到200层,形成一个立方体集成电路。

有人可能会问,形成立方体后,还可以堆叠更多吗?理论上讲是可以,但一般来说,我不建议,原因在后面讲述。

在Cubic IC的设计方法学中,整个芯片的最大厚度尽可能不超过芯片的长(宽),也就是,正立方体是其设计和制造的极限,其产品可以是一个扁平的立方体,而不建议是一个柱状的立方体。

因此,我们在设计Cubic IC时,如果设置了芯片的长和宽,当芯片长和宽相等时,其厚度的最大值等于长(宽),如下图A所示的范围。并不是所有的Cubic IC都需要堆叠到一个正方体的形状,可根据实际情况,设计其堆叠层数和厚度,例如下图B所示的范围。

如果立方体的长和宽不相等,则厚度最大值取长宽二者的较小值。不过我建议最好保持长和宽相等,这样芯片的材料利用率会更高。为什么正立方体被设计为 Cubic IC 设计和制造的极限呢?这就牵扯到信号传输距离的问题。我们知道,当信号在平面上传输时,信号在一个周期内可访问到的区域是一个圆。

随着信号频率的升高,圆的半径会逐渐减小,圆的面积可能会小于芯片的面积,也就是说,即使在同一个芯片上,信号在一个时钟周期内也未必能够达到。

这时候,曾经在PCB板级系统出现的内存墙现象在单个芯片上也会出现。

如何能延缓甚至解决这个问题呢?就是向Z轴方向的空间发展。我们可以想象一个动态的过程,如果芯片内的晶体管总量保持不变,在向Z轴发展的过程中,XY轴是在不断缩小的,一直到Z轴的和XY轴相等,形成一个正立方体。这时候信号在整个芯片中传输能耗最小,芯片性能也会最佳。

当Z轴超越XY轴时,由正立方体逐渐变为柱状立方体,芯片整体的能耗不再降低反而会升高,性能也会下降,和我们的设计初衷是违背的。这也解释了上面我们不建议Cubic IC 发展为一个柱状的立方体的原因。

为了能够精确地描述信号在一个周期内可在整个Cubic IC 三维空间内传播的情况,我提出了一个李特思空间 LITS 的概念。

四、关于李特思空间 LITS 的描述

李特思空间 LITS 是一个介于理想和现实之间的空间,严格来说是介于理想传输和现实传输之间的空间。

李特思空间 LITS 全称为:Li's Isochronous Transmission Space,李氏等时传输空间,简称为LITS,中文音译为“李特思空间”,也寓意着我进行了特别的思考而得出的空间。这次,我把自己的姓加上了,是因为我自认为是第一个提出并运用这个空间的,当然如果有人能证明他提出并运用这个空间更早,我自然也会拱手相让。

在了解李特思空间 LITS 之前,我们先了解一下曼哈顿距离和等时传输区域。

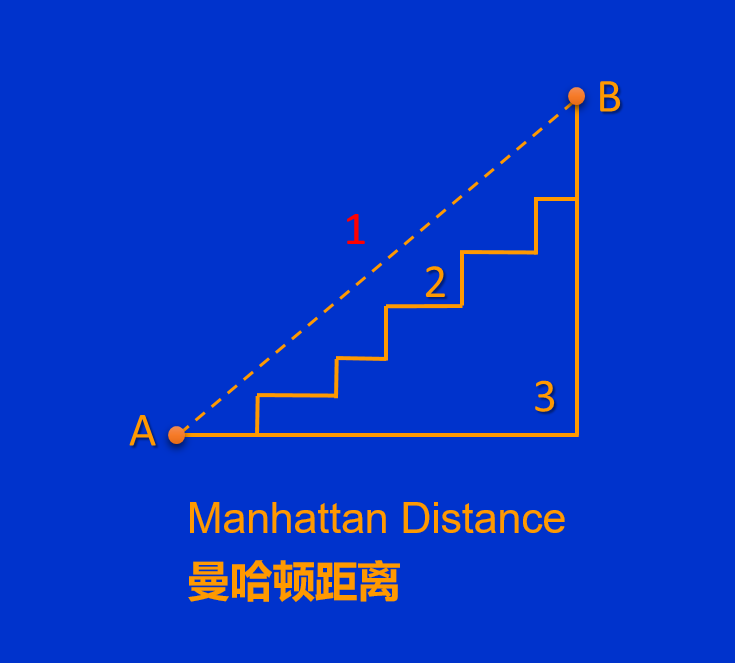

4.1 曼 哈 顿 距 离

曼哈顿距离是由赫尔曼・闵可夫斯基所创立,用以标明两个点在标准坐标系上的绝对轴距的和。这位赫尔曼可不是别人,正是爱因斯坦的老师,那位创立了四维时空概念的闵可夫斯基。

曼哈顿距离的正式意义为,在欧几里德空间的固定直角坐标系上两点所形成的线段对轴产生的投影的距离总和。

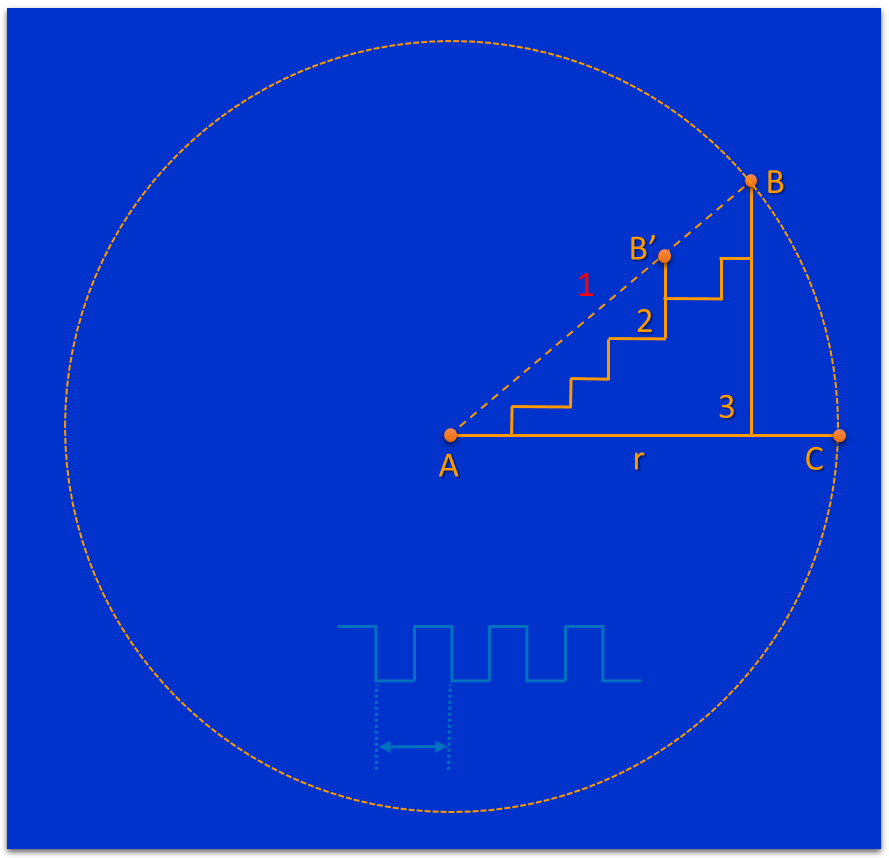

在XY平面上,曼哈顿距离如下图所示,即A点和B点之间的曼哈顿距离为,两点之间的直线距离在X轴和Y轴投影之和。

4.2 等 时 传 输 区 域

在第三节中,我们讲到,当信号在平面上传输时,信号在一个周期内可访问到的区域是一个圆。而实际情况并非如此,问什么呢?

因为在实际的芯片的布线中,布线基本都是横平竖直的,下图所示为某存储芯片的金属布线1000倍显微图像,可以看出,所有的布线都是横平竖直的。

因此,我们可以得出,在芯片中从A点到B之间的物理布线距离,实际就是曼哈顿距离。那么,在相等时间内,信号在芯片上向不同方向传播,可传输的距离范围就不是一个圆,那会是什么样的图形呢?

下面,我们详细分析一下。

例如在一个时钟周期内,信号在芯片平面上可传输的距离为 r,以 r 为半径的圆是信号在理想情况下可传输的距离范围。例如圆上的C点和B点。因为芯片上的实际布线遵循着曼哈顿距离布线的原因,同一个时钟周期C点可以到达,而B点是不能到达的,只能到达中间的B’点,如下图所示。实际的布线路径也不会是1所代表的虚线,而可能是2代表的路径。

以A点为原点构建坐标系,根据曼哈顿距离的定义,C点和B’点都满足其X坐标和Y坐标的投影之和相等,我们可得到等式:x + y = r,扩展到其它象限,我们可得出 |x|+|y|= r,四个象限的线段刚好组成了一个倾斜角为45度的正方形。

由此,我们可以得出,在芯片面积内,虽然在相等时间内(某一个时钟周期),理想的传输距离范围是一个圆,而实际的传输范围是一个45度倾斜的正方形。

有一些特殊情况,例如芯片上的布线不完全遵循曼哈顿距离布线,而是部分走了斜线,则传输的距离位于45度倾斜的正方形和其外接圆之间的区域。我们可称之为等时传输区域 Isochronous Transmission Area,可简称为ITA。

4.3 LITS 空 间

在本文中,我们描述的主要对象是立方体集成电路 Cubic IC,信号的传输距离范围不仅仅在二维平面,而是在三维空间。

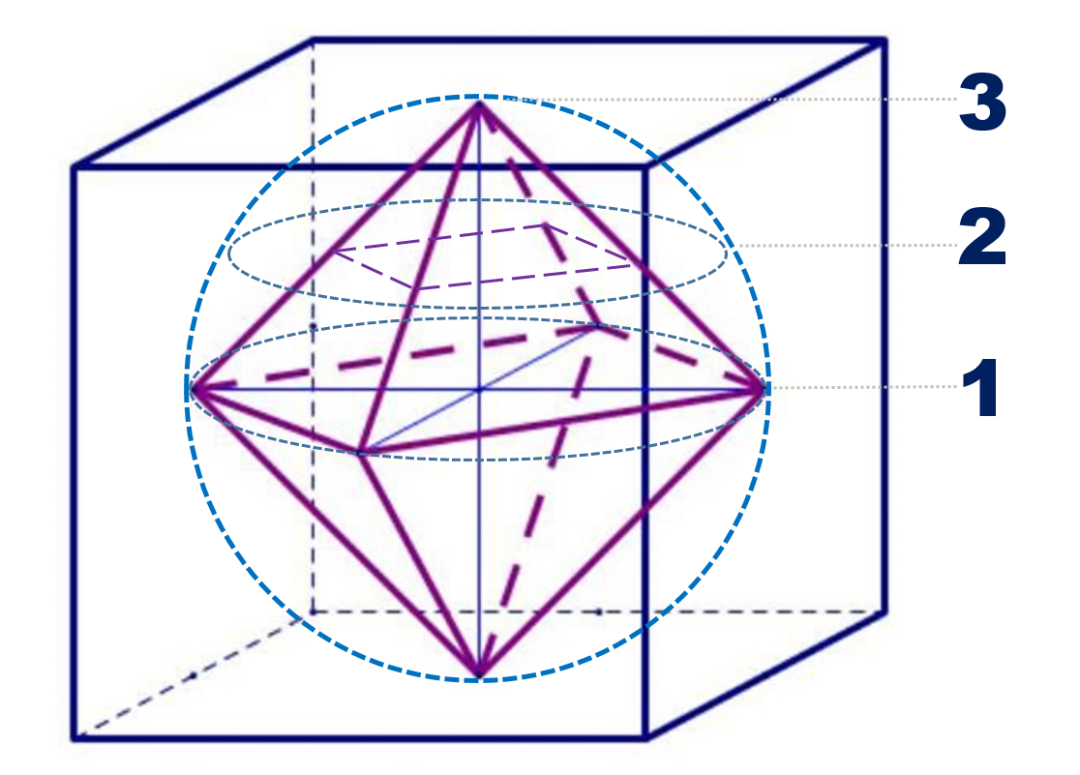

那么,信号在三维空间传输,又会遵循什么样的规律呢?在理想情况下,信号在某一点向空间传播,在相等时间内(某一个时钟周期),理想的传输距离范围是一个球,而实际的传输范围是什么样的呢?在Cubic IC中,其布线的原则同样遵循曼哈顿距离的原则,即沿着X轴Y轴Z轴的方向,因为曼哈顿距离通常应用于平面上的两点,因此,在这篇文章中,空间两点的曼哈顿距离我们称之为空间曼哈顿距离。

在Cubic IC中,从一点出发,以空间曼哈顿距离的方式进行布线,在相等时间内(例如某一个时钟周期),实际的传输距离范围可用方程 |x|+|y|+|z|= r 来描述,这是一个正八面体的表面方程。由此,我们可以得出,在 Cubic IC中,从某一点出发,在相等时间内,实际的传输距离是一个正八面体的表面。而理想的传输距离是一个球的表面。球和正八面体为内外相接的关系。李特思 (LITS) 空间定义:球体与其内接正八面体之间的空间,称为李特思空间,其空间大小为:LITS = 4/3(π-1)r³

该空间占整个 Cubic IC 立方体的空间比为:4/3(π-1)r³÷ (8r³)=0.36

这就是说,在一个虚拟的Cubic IC 立方体内,有36%的空间是从实际等时传输到理想等时传输之间的空间。

这个空间的重要意义在于,在设计Cubic IC 时,可作为在3D空间布局IP单元时的依据或参考。

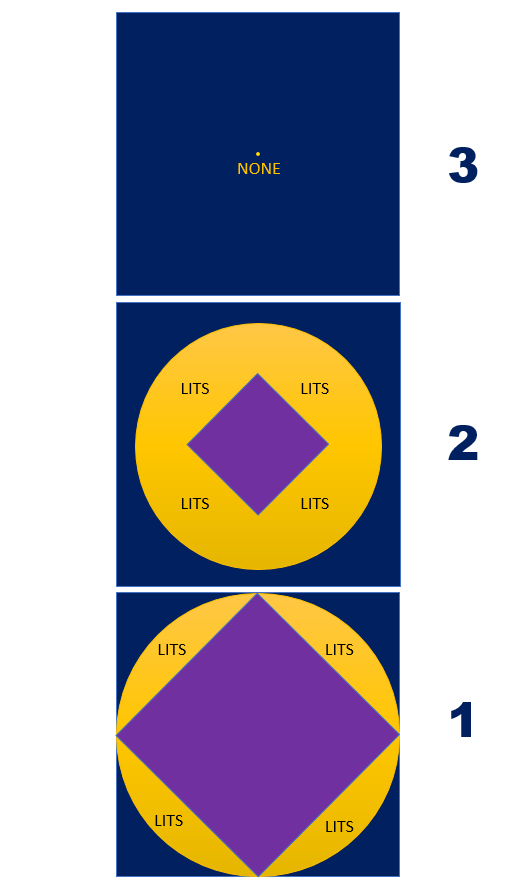

下图所示为LITS空间的图形描述以及在Cubic IC 不同截面的空间大小。

LITS空间在不同截面的大小(金黄色区域)

我们知道,如果严格按照空间曼哈顿距离的方式进行布线,在相等的时间内,只能达到LITS空间的内表面,即正八面体的表面。如果在某些区域允许走斜线,则会进入LITS空间内部,但除了个别点,我们通常无法到达球体的表面,这就是现实和理想之间的距离。LITS空间是一个虚拟的空间,可以作为设计Cubic IC时不同的IP模块布局的参考依据,对于时序等长要求高的模块,尽量安排在LITS空间内表面的附近,从而更容易实现物理上的等长。LITS空间在不同Z轴平面(Storey)上的投影,即可用于对IP模块的位置进行划分。在上面的描述中,我们是以Cubic IC 芯片中心作为参考点的情况,对于其它的关键点,也同样需要构建虚拟的LITS空间,从而精确判断信号传输所造成的延迟,精准地控制信息和指令的传输。

五、关于有效功能体积的描述

在集成电路中,芯片的功能是由一个个晶体管组成的,我们称之为功能细胞Function Cell,由多个功能细胞可以组成功能块Function Block,由多个功能块可以组成功能单元Function Unit。它们统称为功能单位Function UNITs,有这些功能单位可组成微系统MicroSystem、常系统Common System、大系统Giant System。我们知道,无论是微系统、常系统、大系统,电子系统的体积中,功能单位所占的体积只占系统总体积的一部分,而其它的体积,并没有功能,而是作为支撑、保护等因素而存在的。

在本文中,我们将功能单位Function UNITs所占的体积称为有效功能体积EFV (Effective Function Volume)。下面,我们以一颗芯片为例,来解读一下有效功能体积。下图是一个芯片的晶圆侧剖面示意图,从图中我们可以看出,按照定义,有效功能体积包含了晶体管层和布线层,总厚度为约为5um,在布线层的上方是绝缘和保护层,包含聚酰亚胺Polyimide,氮氧化物Oxynitride,未参杂氧化物Undope Oxide,三者总厚度约为5um。

在晶体管层的下方是硅基底,其厚度大约为780~800um。通过计算我们可以得出,上图中,有效功能体积所占的比例仅为芯片总体积的0.625%,还不到1%。

那么,如何提升有效功能体积所占的比例呢?目前常用的方法就是进行晶元减薄。

如果将晶圆减薄到100um,有效功能体积所占的比例为5%,如果将晶圆减薄到50um,有效功能体积所占的比例为10%,如果将晶圆减薄到20um,有效功能体积所占的比例为25%,就此打住吧,因为20um可能是目前减薄技术所能达到的极限了。

通过晶圆减薄,我们使得有效功能体积占芯片总体积比例增加了40倍。如果依此去计算其功能密度,功能密度相当于增加了40倍。许多人正是从这一点上,认为通过先进封装和异构集成技术,还是可以延续摩尔定律的。

然而,事实上,这只是一种假象,不能因为功能密度的增加,就认为摩尔定律是可延续的。从摩尔定律提出的那一刻起,就注定了摩尔定律只是一个区间性的定律,最重要的原因就是摩尔定律曲线是指数增长的曲线,而以指数规律增长的曲线,在物理意义上都是不可持续的。

有了有效功能体积的概念,在设计系统时,从最小的功能细胞Function Cell到最大的大系统Giant System,都应该逐级剖析其有效功能体积,并最大可能地提高有效功能体积所占的比例。

六、Cubic IC 和 3D Chiplet 的区别

Cubic IC看起来和3D Chiplet有些相似,都是将大芯片分割后进行3D堆叠并通过TSV和RDL电气互连。然而,它们有几大不同之处。

为了方便起见,我们后续可以将 Cubic IC 简称为 CIC。

1)CIC 是以三维的视角去设计集成电路,而3D Chiplet则并非从设计一开始就从3D的视角去考虑整个集成电路的设计,通常是先考虑各Chiplet接口之间的匹配,并在制造的时候将小芯片进行堆叠并互连。

2)CIC 不同的楼层(Storey)尺寸是完全相同的,堆叠后形成立方体形状,3D Chiplet可以由不同尺寸的Chiplet组成。

3)CIC 是对未来集成电路设计和制造的预期,3D Chiplet是目前先进封装和异构集成可以实现的技术。

4)Chiplet是IP芯片化的设计思路,将不同的IP分割成小芯片后在封装级别进行集成,CIC并不需要将不同的IP分割,而是将这些IP合理地分配到不同Storey的不同区域。

5)CIC 的楼层(Storey)数量可以堆叠到几百层,3D Chiplet目前堆叠的层数是个位数。

6)CIC 对EDA工具的要求很高,目前还没有任何一家EDA工具可以支持,需要后续EDA厂商的积极研发,3D Chiplet对EDA工具的要求相对不高,目前的先进封装设计工具例如XSI+XPD就可以很好支持了。

7)CIC 的功能密度要远高于3D Chiplet,因此其实现的难度和挑战都要远远高于3D Chiplet。对此,我们可以这么理解,CIC是3D Chiplet甚至整个IC集成电路发展的终极目标,而3D Chiplet则是CIC发展的初级阶段。

七、关于 Cubic IC 制造方法的预期

我们知道,虽然芯片制造非常复杂,可细分为几千道工艺,但总的来说,可分为三种类型:加工艺、减工艺和辅助工艺。加工艺也可称为增材制造,即通过不断地增加不同的材料,而完成最终的产品。3D打印就是一种典型的增材制造。在芯片制造中,溅射、离子注入就属于加工艺。减工艺也可称为减材制造,芯片制造中,最典型的减工艺就是刻蚀。至于光刻,虽然极其重要,其实是属于辅助工艺,因为光刻就是辅助将图形印刷在了晶圆上,并不会使晶圆上的材料增加或者减少。

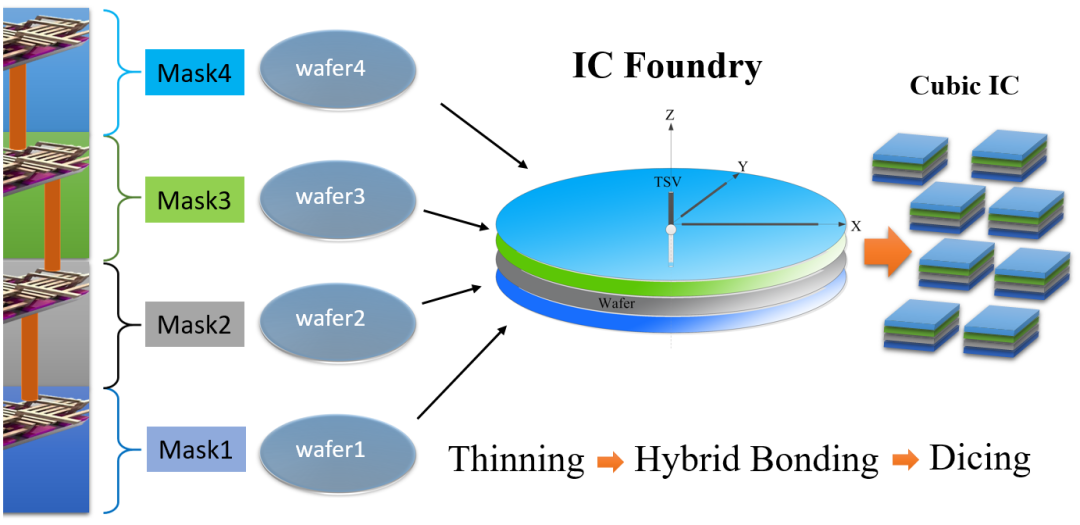

对于CIC的制造方法,我看可以参考下面一张图,每一个楼层Storey生成相应的掩膜,和传统的IC制造方法一样,进行光刻、刻蚀、气相沉积、离子注入、研磨、清洗等操作,然后将每个Storey的晶圆进行减薄Thining,通过混合键合Hybrid Bonding的方式将晶圆键合到一起,最后进行切割,得到CIC。

下面,通过实际产品的数据估算,了解 CIC 技术可能带给集成电路产业的提升!我们就用一个具体的实例进行分析,并描述CIC的巨大优势。2019年8月20日,美国创企Cerebras的巨型芯片WSE(Wafer Scale Engine)吸引了足够的眼球,这款芯片的尺寸达到了惊人的46225 平方毫米,每边约21.5厘米,比iPad还要大。Cerebras WSE是世界上第一款晶圆级处理器,在一个12寸 (300mm) 的晶圆上只能做出一个芯片。WSE的惊人参数还包括,拥有1.2 万亿个晶体管(同时代的主流芯片都还在百亿级别),并且拥有40万个AI核心、18GB SRAM缓存、9PB/s内存带宽、100Pb/s互连带宽等,此外,其功耗为1.5万瓦,超过6台电磁炉的功率,同样震撼了行业。WSE采用台积电16nm工艺制造,可以用于基础和应用科学、医学研究,充分发挥其超大规模的优势,与传统超级计算机合作,加速AI工作。由于WSE芯片工作的功耗过6台电磁炉的功率,可以毫不夸张地说,这款芯片一工作起来完全可以供几十人一起围着吃火锅了。

2021年4月,Cerebras 再接再厉,推出了新的WSE-2处理器,采用台积电的 7nm 工艺,具有破纪录的 2.6 万亿个晶体管, 85 万颗 AI 优化内核,和一代保持了相同的面积 46225 平方毫米,大小类似餐盘。我们知道,以现有的7nm工艺,在指甲盖大小的芯片上可以集成100亿以上的晶体管,那么,如果以CIC的模式来设计,在指尖大小的1立方厘米内可集成的晶体管数量是多少呢?我们就以晶圆可以减薄到20~40um进行计算,如果以20um计算,1厘米可以堆叠500层,如果以40um计算,1厘米可以堆叠250层。那么,1立方厘米可以集成的晶体管数量为2.5万亿~5万亿,即100亿的250倍~500倍。这样,如餐盘大小 (边长为21.5厘米) 的WSE二代的晶体管数量是2.6万亿,如果按照CIC的设计思路,完全可以在指尖大小的1立方厘米实现了,是不是很让人惊讶?让人很兴奋!

当然会有人说,这只是理论上的情况,实际上设计问题、制造问题、散热问题都有可能解决吗?这正是我们下一节要讨论的内容。

八、Cubic IC 带来的挑战

首先,所有的创新都会带来新的挑战,因此Cubic IC必然带来新的挑战!

8.1 设 计 的 挑 战

设计的挑战主要来自两点,1)对EDA工具的挑战,2)对设计人员的挑战。

首先,我们来分析一下 CIC 带来的EDA工具的挑战,从传统的IC设计转为CIC设计,设计的复杂度会急剧提高。我们现在主流的集成电路,其晶体管上方的布线层可能多达十几层,如果以CIC的方式进行设计,其Storey可能有数百层,这样,组合起来,一个CIC,将会有数百层晶体管,其布线层更是多达数千层。现在看来,这对EDA工具的挑战是极大的。

同时,为了增加工艺灵活性,CIC允许不同的Storey(楼层)采用不同的工艺节点制造,例如Storey1采用7nm工艺,Storey2采用5nm,Storey3采用14nm,Storey4采用28nm工艺...... 需要在一个项目中管理多种工艺节点数据,也给EDA工具带来了挑战。

挑战的同时也带来了机遇,任何一家的EDA工具能在CIC上有所突破并首先占领市场,将成为未来集成电路设计业的霸主!

下面,我们分析一下CIC给设计人员带来的挑战。

从上面第七节的描述我们得知,在7nm工艺下,指点大小的1立方厘米尺寸的CIC,其集成的晶体管数量大约在2.5万亿~5万亿,随着工艺节点的缩小,加上CIC体积的增大,两种因素叠加起来,其晶体管数量可能超越100万亿,是现在主流芯片的一万倍,海量的数据如何处理,是带给设计人员和设备的重大挑战。

电磁干扰的问题,在1立方厘米中集成了2.5万亿~5万亿的晶体管,在功能密度极大化的同时,会不会带来电磁干扰的问题,也是设计人员需要重点考虑的。

不过也不用过于担心电磁干扰问题是由于堆叠层数太多而引起的,以现在成熟的7nm工艺,芯片间的互连布线间距最小在20~40nm左右,而以目前最先进的减薄工艺,可将晶圆减薄到20~40um,通过混合键合后,上下层晶体管的距离约为20~40um,可以看出,同一个Storey布线的间距和不同Storey的间距之间还有三个数量级(1000倍)的差别。因此,即使存在电磁干扰问题,也会先在同一个Storey出现,而解决方法和现在成熟的集成电路相仿即可。

8.2 制 造 的 挑 战

在负责的产品设计的过程中,我非常重视和工艺人员的交流。尤其是包含有新方法和工艺的情况下。因为再优秀的设计,如果不能够制造出来,也只会是海市蜃楼,仅仅看上去很美。

CIC是集成电路设计的新思路,必然包含新工艺和新方法,因此,能否制造出来是最为关键的环节。

首先是每一个Storey的制造,这和传统的IC制造方法并没有特别大的区别,最主要的区别是在每个晶圆上事先要将进行Storey之间互连的TSV制作出来。并且要保证不同的Storey之间互连的对准,如果由于结构原因,上下层Storey的TSV无法对准,则需要通过RDL来进行辅助对准。

然后,就是Storey之间的键合,现在有了混合键合工艺Hybrid Bonding,互连间距可以缩小到10um,相当于在1平方毫米可以多达10000个互连,在未来,Hybrid Bonding可支持每平方毫米100万个互连,这样的互连密度,是可以满足CIC的需求的。

8.3 散 热 的 挑 战

最后,我们来看看散热带给我们的挑战。

以CIC的思路去设计集成电路,必然会形成空间功能密度的极大化,而晶体管数量的剧增必然带来热量的增加,如何把这些热量散发出去呢?

首先,我们要相信,这个问题是可以解决的!

让我们先回顾一下芯片耗能和散热的历史。在2001年的国际固态电子电路会议上,专家们曾经指出,如果芯片耗能和散热的问题得不到解决,到2005年芯片上集成了2亿个晶体管时,就会热得像“核反应堆”(1000℃),到2010年时就会达到火箭发射时喷嘴的高温水平(3000℃),而到2015年就会与太阳的表面一样热(6000℃)。

20年过去了,我们手机中的处理芯片晶体管数量已经达到了百亿级别,芯片的温度既没有像太阳表面一样热,也没有达到火箭喷嘴的水平,更不用担心手里的握着“核反应堆”。目前我们手机里的主要芯片晶体管数量都在100亿量级,是专家们曾经预测的50倍,依然可以稳定地工作,手机拿在手中,大多数时间我们甚至都很难感受到芯片发出的热量。可见芯片工程师的智慧还是可以相信的。

具体如何芯片耗能和散热的问题,主要从两大方面考虑,1)降低芯片功耗,2)降低散热通道的热阻。降低芯片功耗可以从动态功耗、静态功耗、传输功耗三个方面入手;降低散热通道的热阻可以从新传热材料、新散热结构两方面考虑,限于篇幅关系,这里就不展开讨论了,后续的文章会有相应的专题。

A Brand New Idea of IC Design

九、Cubic IC 能否延续摩尔定律

在新书《基于SiP技术的微系统》中,我曾经写过这样一句话:”所有按照指数规律增长的曲线,从物理意义上来讲,都是不可持续的“。摩尔定律恰恰是按照指数规律增长的曲线,因此在物理意义上是不可持续的。

从而我们得出,即使Cubic IC成为现实,也是不可能延续摩尔定律的!

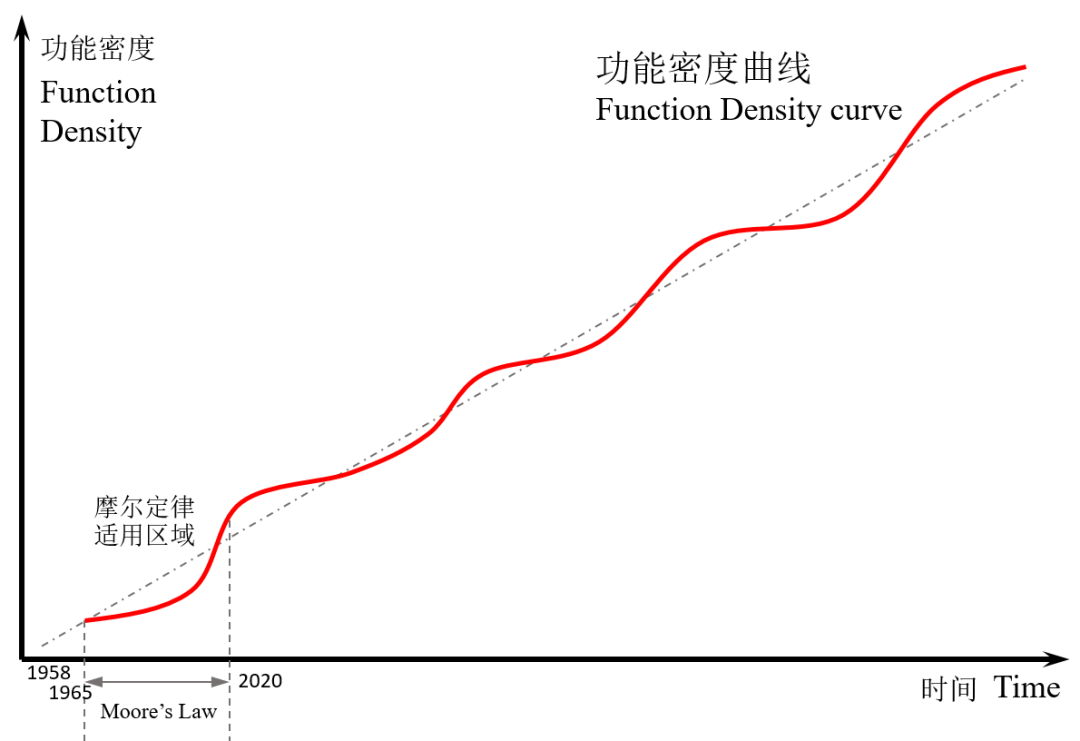

为此,作者在新书中提出了电子集成技术普遍适用的一条规律:”功能密度定律“,并预测了功能密度定律曲线,如下图所示。

从曲线中我们可以看出,在电子集成技术发展的初期(1958~2020年) ,电子系统的功能密度随时间的变化是按照摩尔定律增长的,其曲线呈现指数增长趋势。随着摩尔定律的逐渐失效,其曲线逐渐平缓,但依然保持增长。

从长远来看,功能密度曲线是一条单调增长的波动曲线,随着新技术的不断涌现,在不同的历史阶段,其增长的斜率是不同的,甚至在某些特定的区间,可以以指数规律进行增长。

功能密度定律:对于所有的电子系统来说,沿着时间轴,系统空间内的功能密度总是在持续不断地增大,并且会一直持续下去。Function Density Law:For all electronic systems, along the time axis, the Function Density in system space is constantly increasing and will continue.

总 结

这篇文章中提到的几个重要概念:如立方体集成电路CIC,等时传输区域ITA,李特思空间LITS,有效功能体积EFV,均为本文作者首次提出,能否为业界所认可并逐渐接受,并由“新思路”成为一种现实的设计方法,现在下定论有些为时过早,还需要时间来检验。

如果这篇文章中提到的“新思路”能在未来成为现实,其中包含的概念和技术能成为集成电路设计的新方向,那么,提早上车并启动或许是实现弯道超车的可行途径。CIC的设计与制造,是一个非常难以实现的目标。但如果要在竞争中胜出,就必须努力去实现!这就是目标的力量。有的人因为看见而相信,有的人因为相信而看见。 这是一篇万字长文,我用了很久的时间来进行思考、假设、求证、撰写。读者读到这里,我想也一定花费了不少时间,希望你有所收获,有所感悟!最后,我们可以用一句话总结这篇文章:“在立方体内雕刻晶体管,Sculpt Transistors in Cube” ―― Suny Li(李扬)